New trends such as autonomous driving, connectivity, and infotainment are dominating the automotive evolution. The transmission requirements and data payload on automotive networks continues to increase significantly. This is also impacting the internal car architecture substantially where the new Automotive Ethernet plays a key role within the automotive busses. To take this next step while ensuring safety and security, the right ESD protection needs to be in place. With dedicated ESD protection devices from Nexperia, the circuit design will reach the next level of robustness against destructive electrostatic discharge. The System-Efficient ESD Design (SEED) which is a system-level approach to ESD simulations has helped develop new protection components that meet industry requirements.

As mentioned in a previous blog, ‘OPEN Alliance: Get the right ESD protection placement’, to support the rising demands of high data-rates, data security and flexibility a shift from heterogeneous in-vehicle networks (LIN, CAN-FD and FlexRay) to a homogeneous Ethernet architecture is required.

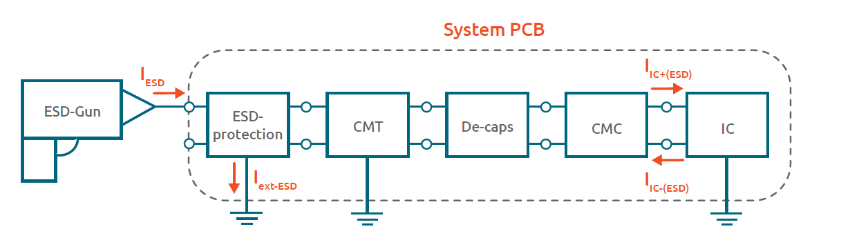

One key goal of the OPEN Alliance (One-Pair Ether-Net) Special Interest Group (SIG) is to enable the deployment of the existing IEEE 100BASE-T1 and 1000BASE-T1 physical layer specifications with complementing specifications for conformance and interoperability. To achieve that while addressing the unique operating conditions in cars has led in the first place to higher trigger voltages of the external ESD protection. This allows the ESD protection to be very robust against external electromagnetic noise which can be present in a harsh automotive environment. Moreover, the position of the ESD protection device next to the connector – rather than between the common-mode choke (CMC) and the PHY – is the key and allows to protect not only the PHY but also the CMC and the passives.

In its documents ‘IEEE 1000BASE-T1 EMC Test Specification for ESD Suppression Devices’ and ‘IEEE 100BASE-T1 EMC Test Specification for ESD Suppression Devices‘, the OPEN Alliance proposes a measurement called ‘ESD Discharge Current Measurement’ which is mandatory for the ESD protection devices for 1000Base-T1 and 100Base-T1, respectively . This very specific test gives an estimation of the overall system-level ESD robustness determining the residual current into the PHY and identifying the ESD robustness class according to human body model requirements for the IC (PHY).

SEED provides system-level approach to predict ESD robustness

A fundamental ESD design challenge is the prediction of system level robustness. A general misconception is that system level ESD robustness depends on the robustness of individual components. Instead, it depends on several factors:

- robustness of the weakest device in the system (usually the SoC that is to be protected)

- properties of the protection device

- properties of other elements in the signal path

- parasitic effects arising from the board and mounting wires

The concept of SEED (as outlined in Chapter 5 of the ESD Application Handbook – Protection concepts, testing and simulation for modern interfaces) is to consider all these parameters as an equivalent circuit or circuit-like SPICE based simulation to predict system level ESD robustness. An equivalent circuit representation of the system, including the SoC, relates to a dedicated dynamic transient SEED model of the ESD protection component to evaluate the overall system ESD performance. In addition to the SPICE-based simulations, other simulation tools such as Verilog-A and customized models based on network parameter blocks can be combined to realize the system.

OPEN Alliance Ethernet ESD protection

When developing the industry’s first silicon-based, OPEN Alliance-compliant ESD protection for 100/1000BAASE-T1 automotive Ethernet systems, Nexperia used System-Efficient ESD Design (SEED) methodology to replicate the ESD Discharge Current Measurement test.

By using the SEED methodology, Nexperia was able to investigate how different parameters, including the parasitic inductance of the external ESD protection device, its trigger and snap-back behavior, influence the system level ESD robustness. It also enables developers to predict the levels of electromagnetic stress that other passive devices are exposed to during an ESD event. A full description and explanation of how the methodology was applied can be found in our whitepaper: Efficient prediction of ESD discharge current according to OPEN Alliance 100BASE-T1 specification using SEED.

The result is the first true OPEN Alliance-compliant ESD protection for 100/1000BASE-T1 Ethernet. Silicon devices offer a significantly higher level of protection - up to 30kV system level robustness – than older technologies such as varistors, which are also subject to degradation over time. Available in very compact and reliable leadless packages such as DFN1006 but also in established SOT23 surface-mounted plastic packages, the PESD2ETH1GXT-Q, PESD2ETH1G-T and PESD2ETH100-T for dual-line as well as PESD1ETH1GXLS-Q and PESD1ETH1GLS-Q for single line ESD protection are the first choice for modern automotive Ethernet interfaces also applicable in Multi-Gbit Range.